在過去的幾十年中,半導體的發(fā)展一直列為重中之重。半導體芯片已經(jīng)發(fā)展成為支持多種應用的核心技術(shù)。它們在移動設備中的成功實施加速了市場需求,并建立了一個業(yè)務平臺來推動持續(xù)創(chuàng)新和性能改進,并擴展到監(jiān)控、醫(yī)療和汽車行業(yè)。不同芯片堆疊架構(gòu)的性能屬性。直接鍵合之后的 Via-last 硅通孔 (Via-last TSV) 和混合鍵合 (HB) 技術(shù)被認為是用于傳感器芯片堆疊的更新和有利的芯片到芯片互連技術(shù)。半導體芯片應用于高性能計算、高頻通信和其他應用,倒裝芯片互連的增長依然強勁,銅柱互連技術(shù)的使用也越來越多,還要最先進的超高密度互連可制造性。那么,品質(zhì)要求也越來越高。

半導體芯片推力的大小取決于芯片的結(jié)構(gòu)、材料、電流、電壓等參數(shù),一般需要進行詳細的設計和測試才能確定。半導體芯片推力的應用范圍很廣,例如在衛(wèi)星姿態(tài)控制、飛行器姿態(tài)控制。

半導體芯片推力計算方法如下:

半導體芯片推力的計算需要考慮多個因素,包括芯片的結(jié)構(gòu)、材料、電流、電壓等參數(shù)。一般來說,可以通過以下公式計算半導體芯片的推力:

F = K * I * B * L

其中,F(xiàn)表示推力,K為常數(shù),I為電流,B為磁感應強度,L為導體長度。這個公式是基于洛倫茲力的原理,即當電流通過導體時,會受到磁場的作用而產(chǎn)生力。

在實際應用中,還需要考慮芯片的具體結(jié)構(gòu)和材料特性,以及外部環(huán)境因素。因此,需要進行詳細的設計和測試,才能確定半導體芯片的推力。

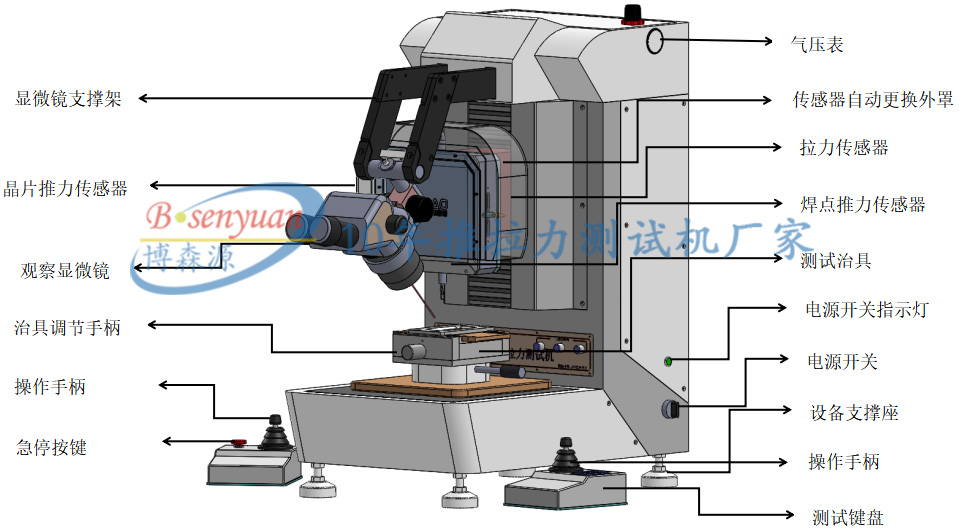

以博森源電子研發(fā)生產(chǎn)的LB-8600半導體芯片推拉力測試機為例,配備正版軟件,測試數(shù)據(jù)(力值、平均值、Cpk,Cp)實時導出與保存,省去繁瑣的計算過程和避免數(shù)據(jù)錯誤。根據(jù)測試要求的不同,選擇不同規(guī)格的模組。采用旋轉(zhuǎn)式三工位獨立傳感采集系統(tǒng),設備配標準配置或根據(jù)客戶提出的要求。

產(chǎn)品細節(jié):

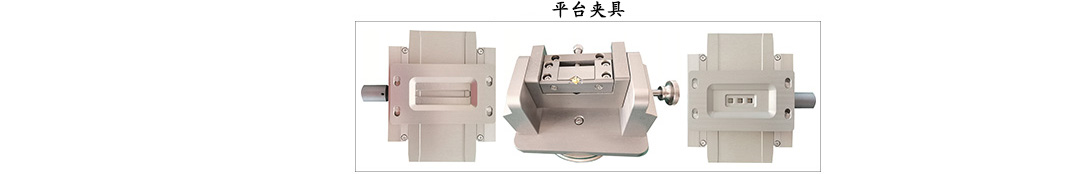

可選配件:

PS:夾具考驗公司工程師的水平

以上就是關(guān)于半導體芯片推力如何計算的相關(guān)介紹,這里需要注意的是,測試室應該保持干燥、溫度適宜、無塵等條件。測試過程中應該注意安全,避免電流過大、電壓過高等情況,以免發(fā)生人員安全事故。